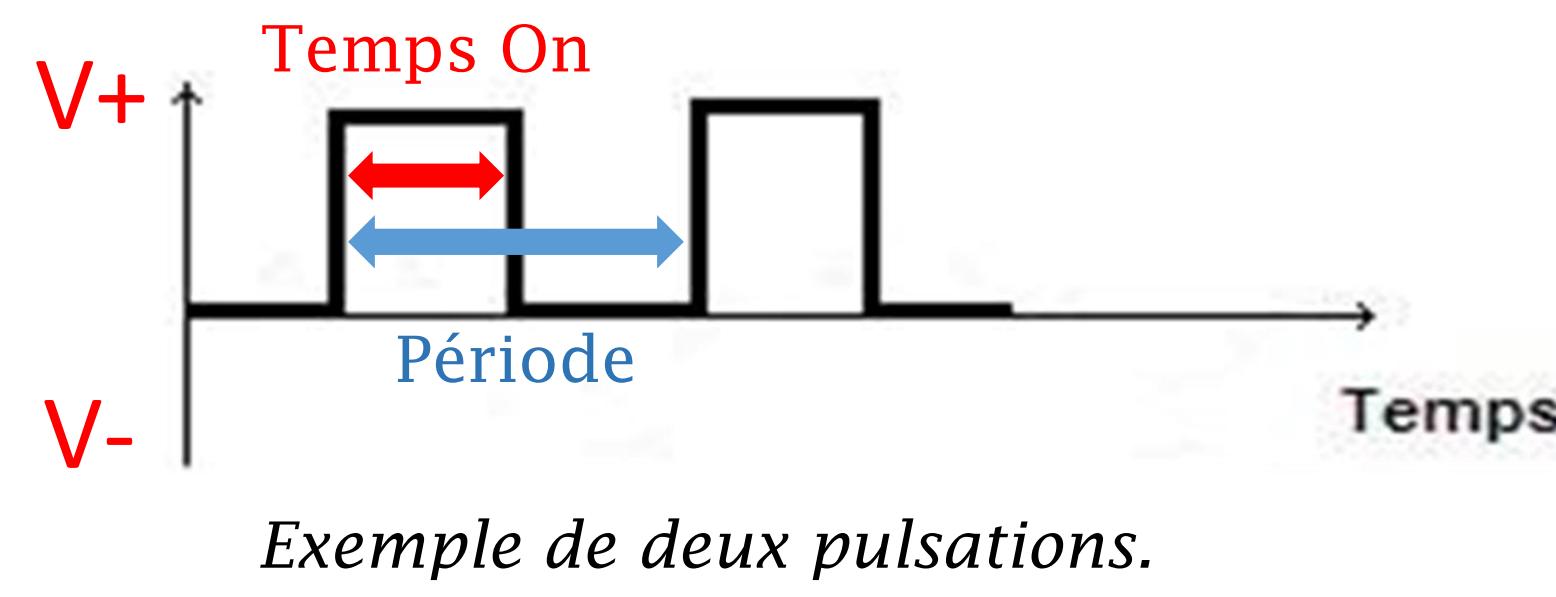

Ce projet a pour objectif de générer des pulsations électroniques, négative ou positive, allant de 0 volts à V+ pour les pulsations positives, et de 0 à V- pour les pulsations négatives. Il doit aussi permettre à l'utilisateur de choisir l'amplitude du signal compris entre V+ et V-, de choisir le nombre de pulsation et le temps à l'état haut (Temps On) par rapport à la période qui doit être compris entre 100 ms et 1 us.

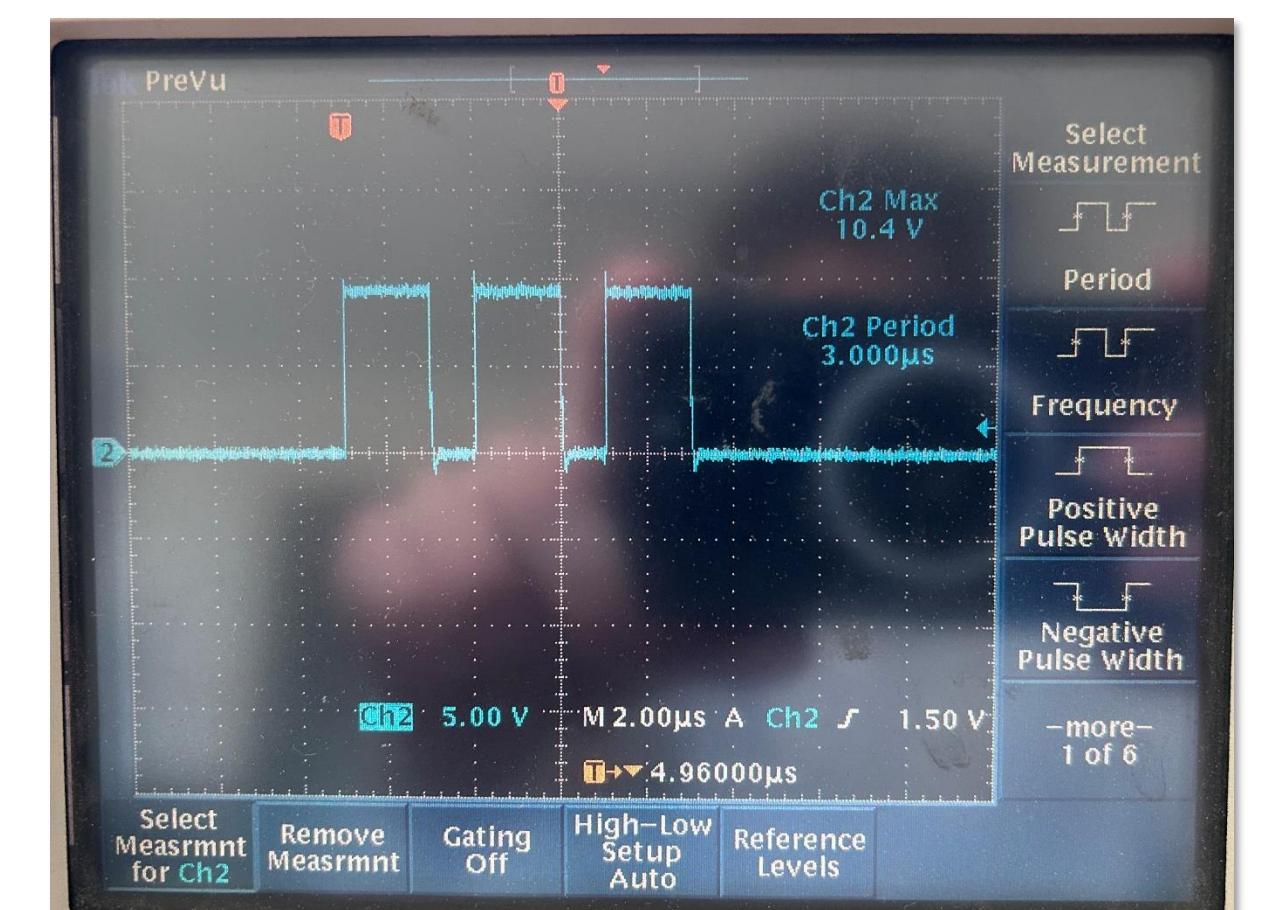

Exemple d'un cas réel avec 3 pulsations qui ont un temps On de 2 us sur une période de 3us pour une amplitude de 10V.

Le but de ce projet est de permettre aux chercheurs de contrôler les propriétés électriques et magnétiques d'une nanostructure durant son étude par microscopie électronique en transmission. Ce contrôle nécessite l'injection in situ de pulses électriques sur l'échantillon placé à l'intérieur du microscope

Par exemple: Retournement de la polarisation ferroélectrique d'une couche mince ou déplacement de parois magnétiques dans un nanofil d'un site de piégeage à un autre.

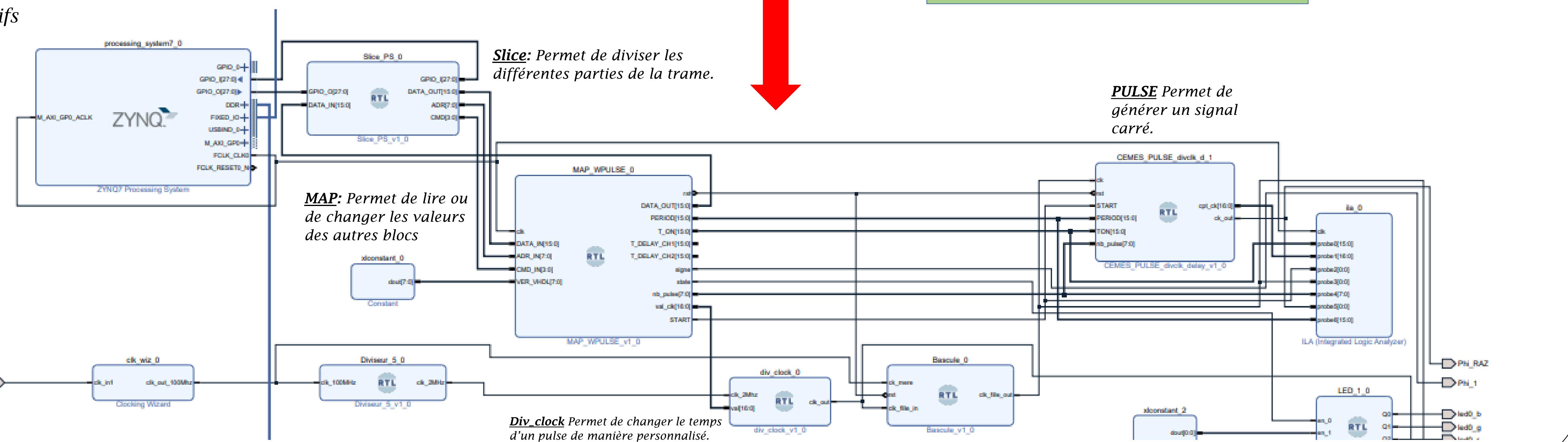

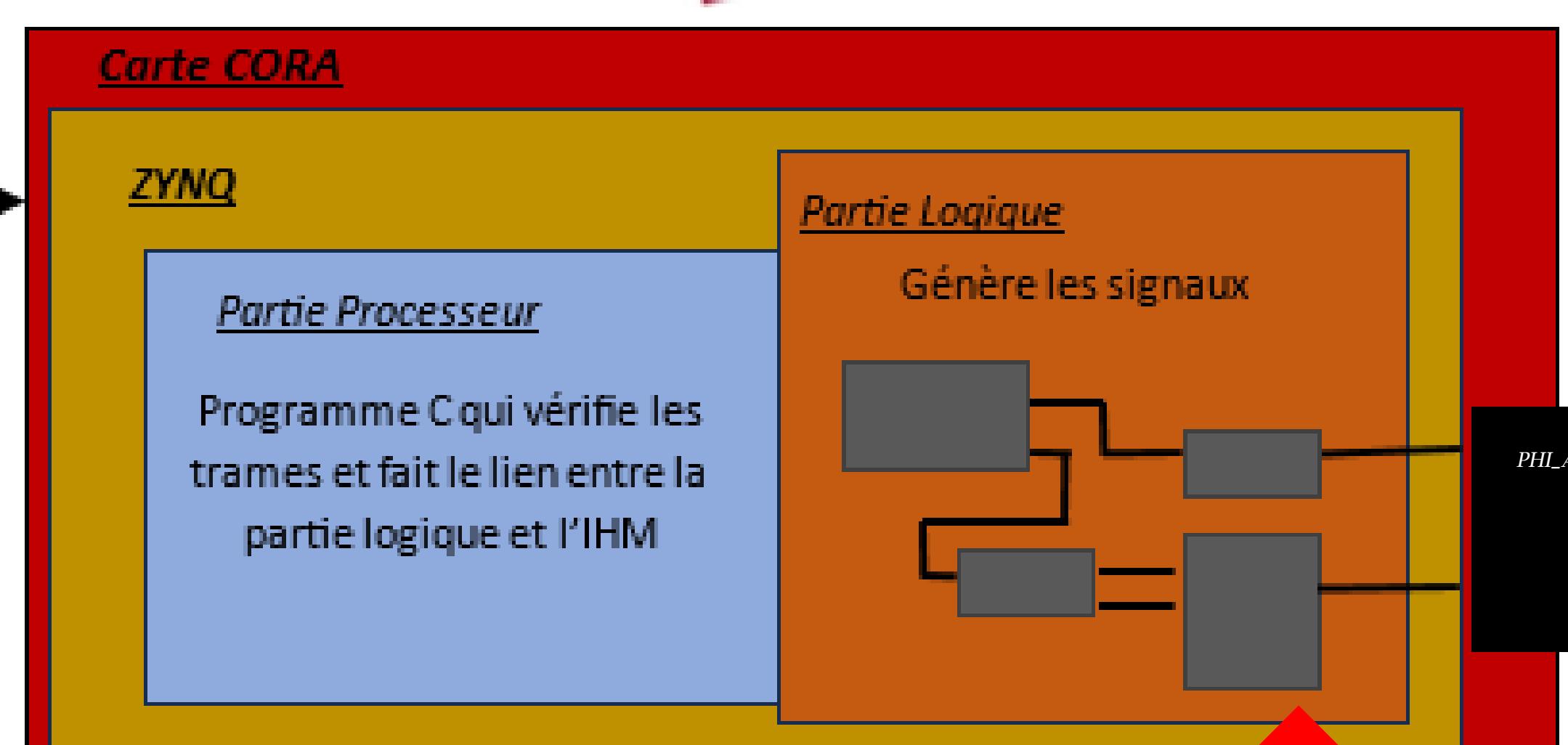

Programmation sur un ZYNQ qui allie à la fois un processeur et un FPGA, pratique pour programmer à la fois la partie hardware et atteindre des vitesses bien supérieures.

#### Avantages:

- Projet fait sur mesure.

- Ultra rapide.

#### Langages de programmation:

- C/C++

- VHDL / Verilog

#### Caractéristiques:

- **Cœurs ARM** : 1 cœur Cortex-A9 cadencé à 667 MHz

- **Mémoire vive** : 512 Mo DDR3L, bus 16 bits à 1050 Mbps

- **Stockage** : emplacement pour carte microSD

- **Logique programmable**: 2 blocs de gestion d'horloge

- 225 Ko de mémoire RAM bloc

- 28 800 bascules (flip-flops)

- **Alimentation** : via USB ou source externe de 4,5 V à 5,5 V

- **Environnements de développement compatibles** : Xilinx Vivado

Carte CORA Z7-S7

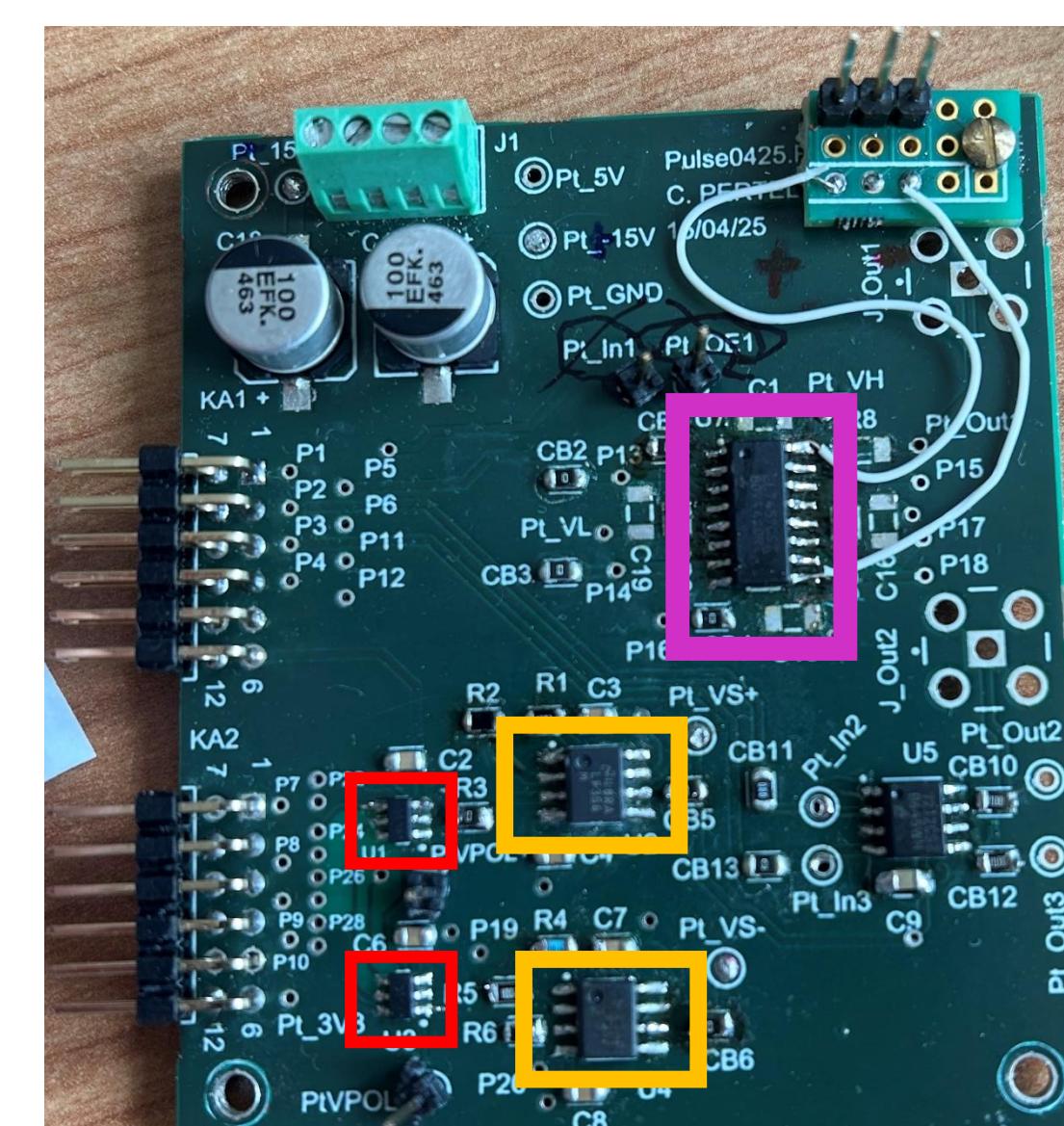

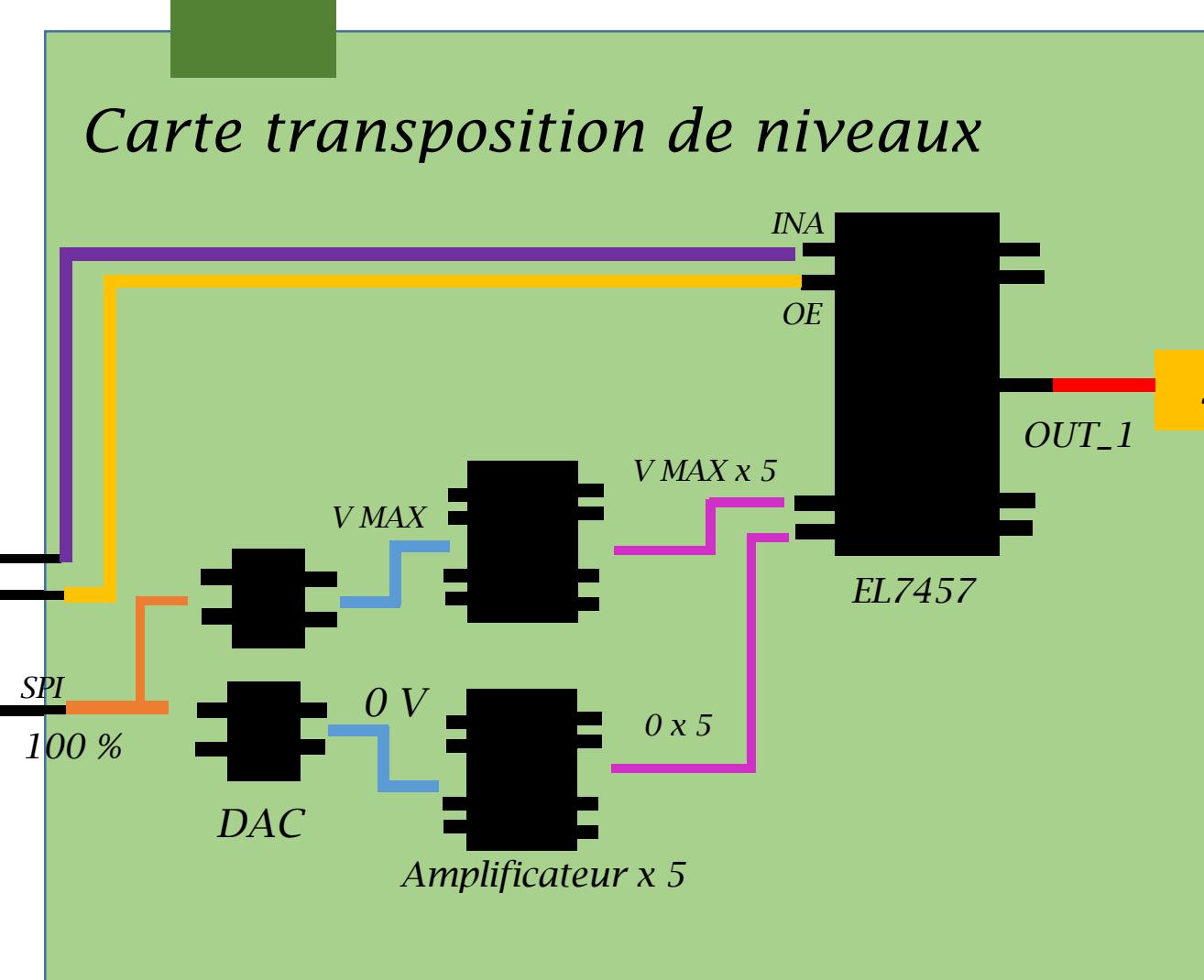

La carte transposition de niveaux a pour but de fixer les tensions de sortie générées par la carte Cora pour ensuite obtenir une tension de sortie compris entre V+ et V- (Max = +10V, -5V).

Carte transposition de niveaux

Le niveau de tension de sortie est généré par les **DAC** (Convertisseur numérique analogique) puis amplifié par des **AOP** (Amplificateur Opérationnel) avant d'être injecté dans le **EL7457** qui va s'occuper de transposer les niveau CMOS avec les tension V+, V-.

#### Schéma explicatif :

SW : V1 : TON,0002!

liaison UART

Design Vivado de la partie logique du générateur de pulsation